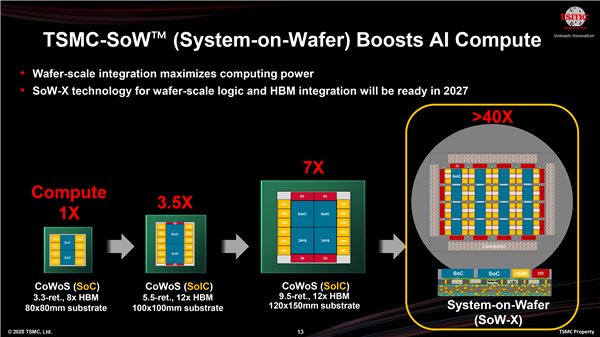

台积电推出高性能多芯片封装技术以应对日益增长的计算需求。该公司计划通过增强其封装能力,支持更大尺寸的高带宽内存组件和高性能计算应用,并在明年或更晚推出下一代CoWoS-L封装技术。该技术将采用面积达4,719 mm²的中介层(约为标准光罩面积的5.5倍),可容纳多达12个高带宽内存堆栈,基板尺寸为100mm×100mm。这一解决方案不仅能满足英伟达配备12个HBM4堆栈的Rubin GPU需求,还能支持更高性能的处理器,其变体版本将能够构建面积达9.5个标线大小(7,885 mm²)的多芯片组件,基板尺寸为120mm×150mm。

台积电的3DFabric路线图进一步扩展了中介层尺寸,以满足高性能计算和AI应用的需求。这一创新封装技术将极大提升GPU等高性能计算设备的性能,同时在能效方面也展现出显著优势。随着GPU制造商不断探索3D封装技术,通过堆叠多个芯片或Chiplet来实现更高的性能和更高效的计算能力,台积电的技术进步为这一趋势提供了有力支持,进一步推动了高性能计算领域的发展。